the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is a three terminal semiconductor device in which the output the field-effect transistor (FET) is entirely a semiconductor device. the field-effect than applied electric field. Further the current in a FET is entirely due to the original semiconductor device in which the output and is controlled by an applied electric field. Further the current in a FET is entirely due to the original semiconductor device in which the output are in a punction transistor both majority and minority consists whereas in a junction transistor both majority and minority consists. is controlled by an adjunction transistor both majority and minority carriers contribute to the rily carriers, while the junction transistor is bipolar, a FET is unipolar. There are the carriers while the junction transistor is bipolar, a FET is unipolar. There are the carriers are the carriers while the junction transistor is bipolar, a FET is unipolar. riv carriers while the junction transistor is bipolar, a FET is unipolar. There are two types of the presistors: (i) junction field effect transistor (JFET or simply FET). arrent. Thus, white (i) junction field effect transistor (JFET or simply FET). (ii) metal oxide effect transistor (MOSFET). A JFET can be either of the effect transistor (MOSFET). A JFET can be either of the *n*-channel type or of conductor field effect transistor (MOSFET). A JFET. channel type. We shall here describe an n-channel JFET.

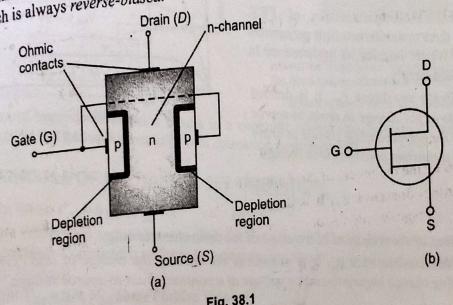

channel JFET. (It consists of a channel (n-type) into which two p-regions are diffused. One of this symmetric structure is called source (S) and the other end is called drain (D). The two of this symmetric connected together to a third terminal called gate (G) (Fig. 38.1). The p-regions are gions are compared to the n-region. During operation, majority, and compared to the n-region. gions are compared to the *n*-region. During operation, majority carriers (electrons in this case) willy doped compared through the source S and leave it through the decir. D. The willy doped company the source S and leave it through the drain D. The current is controlled by gate which is always reverse-biased.

Fig. 38.1

# 38.2 DRAIN CHARACTERISTICS OF AN N-CHANNEL JEET

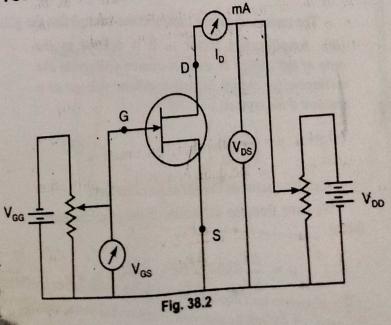

LA curve plotted between drain arrent i<sub>D</sub> and drain-to-source voltage Pos at a fixed gate-to-source voltage s is called the drain characteristics. Fig. 38.2 shows the circuit diagram for determining the output characteristics.  $V_{GG}$  is the gate bias supply and  $V_{DD}$  is be drain voltage source.

Keeping  $V_{GS}$  fixed at some value,  $V_{GG} = \frac{1}{2}$ the drain source voltage (VDS) is changed in steps and the corresponding drain current  $I_D$  is noted. A group of such drain characteristics curves are trawn by setting V<sub>GS</sub> at different fixed

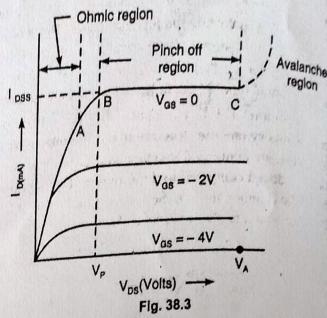

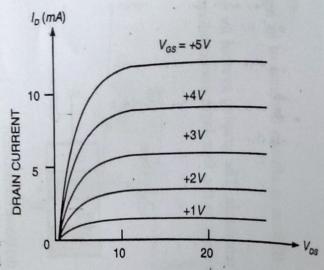

values. Fig. 38.3 shows a family of drain characteristics. There are three distinct regions in the acteristic thus obtained.

(i) When  $V_{DS}$  is small, the channel acts as a resistor. The current increases linearly with the characteristic thus obtained.

(1) When  $V_{DS}$  is small, the channel acts as a resolution of the characteristic is called the ohmic region, voltage  $V_{DS}$  till point A is reached. This region of the characteristic is called the ohmic region, age  $V_{DS}$  till point A is reached. This region of maximum value,  $I_{DSS}$ . If  $V_{DS}$  is increased beyond

(ii) When  $V_{DS} = V_P$ , the current  $I_D$  reaches its maximum value,  $I_{DSS}$ . If  $V_{DS}$  is increased beyond

(ii) When  $V_{DS} = V_P$ , the current  $I_D$  reaches its finding BC is called saturation region or plack off  $V_P$ , the current does not increase any further. The region BC is called saturation region or plack off

region. (iii) At a certain voltage V<sub>A</sub>, corresponding to point C, current increases suddenly due to avalanche breakdown. The covalent bonds in the depletion region break up and the current rises. This region is called the avalanche region. In actual practice this region is to be avoided.

Characteristic parameters of FET. There are three main characteristic parameters of a FET which describe its performance in an electronic circuit.

(i) Drain resistance  $r_d$ . It is defined as the ratio of the change in drain-to-source voltage to the corresponding change in drain current at a constant gate-to-source voltage.

$$r_d = \left(\frac{\Delta V_{DS}}{\Delta I_D}\right)_{V_{GS}} \qquad \dots (i)$$

It is given by the reciprocal of the slope of the drain characteristic.

(ii) Transconductance g<sub>m</sub>. It is defined as the ratio of the change in drain current to the corresponding change in gate to-source voltage at a constant drain-to-source voltage.

$$g_m = \left(\frac{\Delta I_D}{\Delta V_{GS}}\right)_{V_{DS}} \dots (ii)$$

The transconductance measures the control that the gate voltage has over the drain current.

(iii) Amplification factor µ. It is defined as the ratio of the change in drain-to-source voltage to the corresponding change in gate-to-source voltage at a constant drain current.

$$\mu = \left(\frac{\Delta V_{DS}}{\Delta V_{GS}}\right)_{I_D} \qquad ...(iii)$$

Relation between the three parameters.

1 1 1 1/2 8m

We have from the definition of the amplification factor

$$\mu = \frac{\Delta V_{DS}}{\Delta V_{GS}} = \frac{\Delta V_{DS}}{\Delta I_D} \times \frac{\Delta I_D}{\Delta V_{GS}} = r_d \times g_m$$

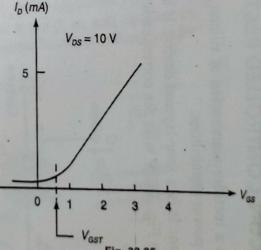

# (ii) Transfer characteristics

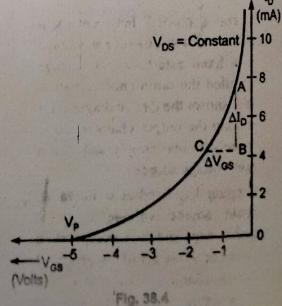

(ii) Transfer drawn between drain current  $I_D$  and gate to source voltage  $V_{GS}$  at constant  $V_{DS}$  is own as Transfer characteristics (Fig. 38.4).

For a constant value of  $V_{DS}$ ,  $I_D$  is noted by varying  $V_{GS}$ . The value of  $V_{GS}$  (-ve) is varied till  $I_D$ For a constant  $V_D$  where  $V_D$  where  $V_D$  is varied till  $V_D$  where  $V_D$  is varied till  $V_D$  compession of the graph gives the transport gight line portion of the graph gives the transconductance g<sub>m</sub>.

Transconductance

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}}\Big|_{V_{DS}}$$

The transconductance is determined from the transfer aracteristic curve.

$$g_m = \frac{AB}{BC} = \text{Slope of the curve.}$$

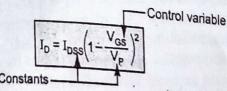

The relationship between  $I_D$  and  $V_{GS}$  is defined by Shockley's

William Bradford Shockley (1910-1989), co-inventor of the first transistor and formulator of the "field-effect" theory employed in the development of transistor and the FET.

(Photo courtesy of AT & T Archives.)

The squared term in the equation results in a nonlinear relationship between  $I_D$  and  $V_{GS}$ producing a curve that grows exponentially with decreasing magnitude of  $V_{GS}$ .

# 38.3 PRINCIPLE OF N-CHANNEL FET OPERATION

Case (i): When  $V_{GS} = 0$  and  $V_{DS} = 0$

When no voltages are applied between D and S and G and S, the thickness of the depletion regions around the p-n junctions is uniform. So a rectangular channel with uniform cross-section is formed [Fig. 38.1 (a)].

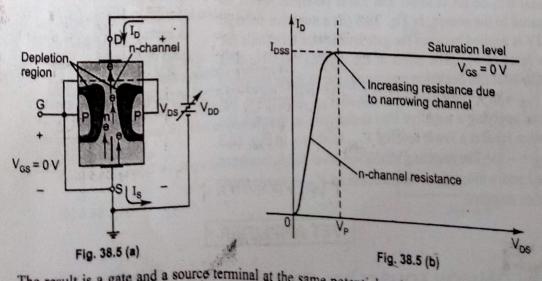

Case (ii):  $V_{GS} = 0 \text{ V}$ ,  $V_{DS}$  Some Positive Value

A positive voltage  $V_{DS}$  is applied across the channel and the gate is connected directly to the source to establish the condition  $V_{GS} = 0$  V [Fig. 38.5 (a)].

The result is a gate and a source terminal at the same potential and a depletion region in the The result is a gate and the distribution of the no-bias conditions of Fig. 38.1 (a). The

instant the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons are drawn to the drain terminal, establishing instant the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons are drawn to the drain terminal, establishing instant the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons are drawn to the drain terminal, establishing instant the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons are drawn to the drain terminal, establishing instant the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal, establishing the electrons are drawn to the drain terminal termina instant the voltage  $V_{DD}$  (=  $V_{DS}$ ) is applied, the electrons of Fig. 38.5 (a). The path of charge flow the conventional current  $I_D$  with the defined direction of Fig. 38.5 (a). The flow of charge flow the conventional current  $I_D$  with the defined direction of Fig. 38.5 (a). The flow of charge is relative. the conventional current  $I_D$  with the defined direction  $(I_D = I_S)$ . The flow of charge is relatively reveals that the drain and source currents are equivalent  $(I_D = I_S)$ . The flow of charge is relatively reveals that the drain and source currents are equivalent of the n-channel between drain and source. The uninhibited and is limited solely by the resistance of the n-channel between drain and source. The depletion region is wider near the top of both p-type materials.

As the voltage  $V_{DS}$  is increased from 0 V to a few volts, the current will increase as determined by Ohm's law. The plot of  $I_D$  versus  $V_{DS}$  will appear as shown in Fig. 38.5 (b). The relative straightness of the plot reveals that for the region of low values of  $V_{DS}$  the resistance is essentially constant. As V<sub>DS</sub> increases and approaches a level referred to as  $V_p$ , the depletion regions will widen, causing a noticeable reduction in the channel width. The reduced path of conduction causes the resistance to increase. The more horizontal the curve, the higher the resistance, suggesting that the resistance is approaching "infinite" ohms in the horizontal region. If  $V_{DS}$  is increased to a level where it appears

M

ph

, ta

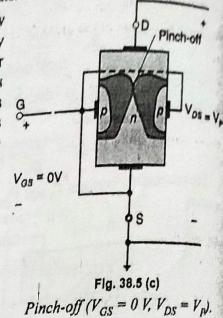

that the two depletion regions would "touch" as shown in Fig. 38.5 (c), a condition referred to as pinch-off will result. The level of  $V_{DS}$  that establishes this condition is referred to as the pinch-off voltage and is denoted by  $V_p$ .

- As  $V_{DS}$  is increased beyond  $V_P$ , the region of close encounter between the two depletion regions increases in length along the channel, but the level of  $I_D$  remains essentially the

- I<sub>DSS</sub> is the maximum drain current for a JFET and is defined by the conditions

$$V_{GS} = 0 \text{ V} \text{ and } V_{DS} > |V_P|.$$

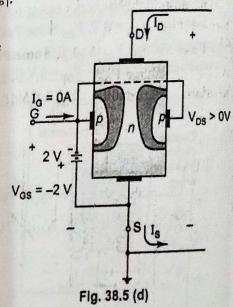

Case (iii):  $V_{GS} < 0 \text{ V}$

The controlling voltage  $V_{GS}$  is made more and more negative from its  $V_{GS} = 0$  V level. In other words, the gate terminal will be set at lower and lower potential levels as compared to the source. In Fig. 38.5 (d) a negative voltage of - 2V is applied between the gate and source terminals for a low level of  $V_{DS}$ . The effect of the applied negative-bias  $V_{GS}$  is to establish depletion regions similar to those obtained with  $V_{GS} = 0$  V, but at lower levels of  $V_{DS}$ . Therefore, the result of applying a negative bias to the gate is to reach the saturation level at a lower level of  $V_{DS}$ , as shown in Fig. 38.3 for  $V_{GS} = -2V$ . The resulting saturation level for  $I_D$  has been reduced and will continue to decrease as  $V_{GS}$  is made more and more negative.

## FET AMPLIFIER

# 38.4 (COMMON SOURCE FET AMPLIFIER

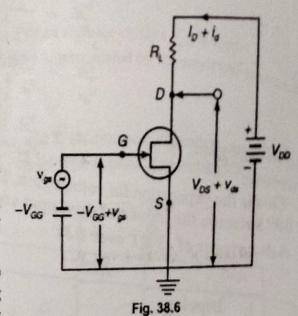

Fig. 38.6 shows the common source amplifier circuit.  $V_{GG}$  is the gate bias battery. The ac signal to be amplified is applied between the gate and the source. The load resistance  $R_L$  is connected with the supply battery  $V_{DD}$  and the drain D. The Taken across the load  $R_L$  or across the FET. the output ac voltage be var for an input signal

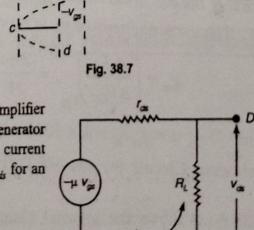

Me l'o working. On applying an alternating signal, fixed reverse bias of the gate changes. A small in the reverse bias gate voltage, produces a change in drain current. This fact makes FET ble of amplifying weak signal. The amplifying of FET can be explained using its transfer eteristics (Fig. 38.7).

When the signal (v<sub>25</sub>) is not applied, the gate to ce voltage is given by OA. The corresponding current is given by OF. When the signal is

which, during the positive half cycle of the input signal  $(+v_{gs})$ , the reverse bias on the gate decreases  $V_{GG} + V_{gg}$ ). The gate to source voltage decreases from OA to OC. Due to this, the channel width reases. Hence, drain current increases from OF to OG. During the negative half of the signal  $(v_g)$ , the reverse voltage on the gate increases  $(-V_{GG} - v_{gs})$  to OB. Due to this the channel width

bereases. Hence the drain current decreases to OE. Thus, a small change in the gate to source olage, produces a large change in drain current and hence large change in output voltage. Thus, FET works as an amplifier.

When the signal voltage is positive, the gate becomes less negative with respect to the source. The drain current is enhanced, causing a large voltage drop across  $R_L$  which makes the drain erminal less positive with respect to the source. Since an increase of the gate voltage causes a decrease in the drain voltage, there is a phase shift of 180° between the input and output of the

### FET amplifier. **Expression for Voltage Gain**

But

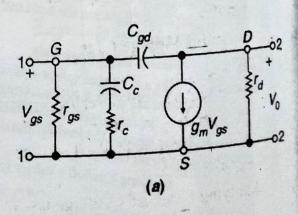

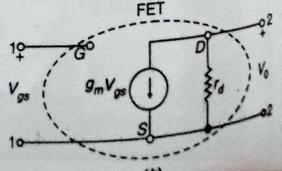

The a.c. voltage source equivalent circuit of FET amplifier is shown in Fig. 38.8. FET can be replaced by a voltage generator  $-\mu v_{gg}$  in series with drain resistance  $r_{dg}$ ,  $i_{d}$  is the ac current flowing through the load  $R_L$ . The output ac voltage is  $v_{ds}$  for an input signal voltage vg

Applying Kirchoff's voltage law to the circuit,  $-\mu v_{gs} = i_d R_L + i_d r_{ds}$

$$i_{d} = \frac{-\mu v_{gs}}{r_{ds} + R_{L}}$$

$$v_{ds} = i_{d} \cdot R_{L}$$

$$i_{d} = \frac{v_{ds}}{R_{L}}$$

$$\frac{v_{ds}}{R_L} = \frac{-\mu v_{gs}}{r_{ds} + R_L}$$

$$\frac{v_{ds}}{v_{gs}} = \frac{-\mu R_L}{r_{ds} + R_L}$$

$$A_v = \frac{v_{ds}}{v_{gs}} = \frac{-\mu R_L}{r_{ds} + R_L}$$

Voltage gain

This is the expression for voltage gain. The negative sign indicates that there is a phase difference of 180° between the input and the output voltages.

Advantages of JFET over BJT

| dvantages of JFET over BJ1                             | FET                                                      |

|--------------------------------------------------------|----------------------------------------------------------|

| BJT                                                    | Unipolar                                                 |

| Bipolar     Input impedance low                        | Input impedance high Voltage controlled                  |

| 3. Current controlled 4. Characterised by current gain | Characterised by transconductance Noise level very small |

| 5. Noise level not small                               | $R_{\rm r} = 500 \ k\Omega$ . If the                     |

Example 1. A common-source FET amplifier has a load resistance  $R_L = 500 \ k\Omega$ . If the a.c. drain resistance  $(r_d)$  and amplification factor  $(\mu)$  of the FET are 100  $k\Omega$  and 24, respectively, calculate the voltage gain of the amplifier.

Sol.

$$|A_{\nu}| = \frac{\mu R_L}{r_{ds} + R_L} = \frac{24 \times 500 \times 10^3}{100 \times 10^3 + 500 \times 10^3} = 20.$$

Example 2. For a constant drain-to-source voltage if the gate-source voltage is changed from 0 to -2 V, the corresponding change in drain current becomes 2 mA. Calculate the transconductance of the FET. If the a.c. drain resistance is  $100 \text{ k}\Omega$ , calculate also the amplification factor of the FET.

**Sol.** The transconductance  $g_m$  is given by

$$g_m = \left(\frac{\Delta I_D}{\Delta V_{GS}}\right)_{V_{DS}} = \frac{2 mA}{2 V} = 1 \text{ mA/V}.$$

$\mu = g_m r_{ds} = 1 \times 10^{-3} \times 100 \times 10^3 = 100.$ Again,

The Equivalent Circuit for the FET (Low frequency model)

Fig. 38.9 (a) shows the internal elements of a FET arranged as a two-port circuit. We can reduce it to a simpler equivalent form as in (b) by consideration of the relative magnitudes of the resistances and the reactances.

The input element  $r_{gs}$  is the reverse – biased junction resistance of a JFET or the silicon-dioxide insulation resistance of a MOSFET. These resistances exceed 108 ohms. We will consider the input of a FET as an open circuit.

**Amplifier**

stage

Rectifier

and filter

Transistor

Fig. 38.15

$$g_d = g_{d0} \left[ 1 - \left( \frac{V_{GS}}{V_P} \right)^{\frac{1}{2}} \right]$$

where  $g_{d0}$  is the value of drain conductance when the bias voltage  $V_{GS}$  is zero. where  $g_{d0}$  is the value of drain condition. The variation of the  $r_d$  with  $V_{GS}$  can be closely approximated by the empirical expression,

$$r_d = \frac{r_0}{1 - KV_{GS}}$$

where  $r_0$  = drain resistance at zero gate bias, and K = a constant, dependent upon FET type. where  $r_0$  = drain resistance at zero gate order waries with applied gate voltage  $V_{GS}$  and  $FET_{acts}$  Thus, small signal FET drain resistance  $r_d$  varies with applied gate voltage  $V_{GS}$  and  $FET_{acts}$

CI

like a variable passive resistor.

FET finds wide applications where VVR property is useful. For example, the VVR can be used in Automatic Gain Control (AGC) circuit of a multistage amplifier.

The VVR is used to vary the voltage gain of a multistage amplifier. If the signal is low then voltage gain of the stages can be increased and when the signal becomes high, the gain can be reduced automatically. In this way, the general level of amplification is maintained fairly constant.

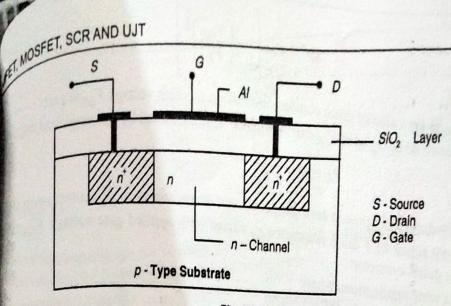

Circuit. Fig. 38.15 shows the circuit arrangement of AGC amplifier using the FET

The capacitor C isolates the transistor from FET so that the bias conditions of transistor are not affected. So, when output increases,  $V_{GS}$  also increases and  $R_{DS}$  changes so that the gain of the transistor decreases. Thus automatically the gain is controlled.

# METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR (MOSFET)

There are two types of MOSFETs.

- (i) The Depletion MOSFET.

- (ii) The Enhancement MOSFET.

In both types, p-channel and n-channel versions exist.

# THE DEPLETION MOSFET

### Construction

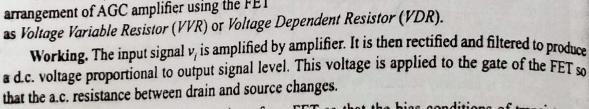

Fig. 38.16 shows the construction of an n-channel depletion MOSFET. It consists of a lightly doped p-type substrate into which two heavily-doped  $n^*$ -regions are diffused. These two  $n^*$  regions act as source S and drain D.

Fig. 38.16

They are separated by about 5  $\mu$ m. A lightlyred n-channel is diffused between the source

of the drain. A thin (~0.1  $\mu$ m) layer of insulating

from dioxide (SiO<sub>2</sub>) is grown over the surface

the structure. Holes are cut into the oxide layer

make metallic contacts with the source and the

min. Then a metallic layer (say, of aluminium)

overlaid on the oxide layer, covering the entire

much region. This aluminium layer acts as gate

7. Simultaneously, aluminium contacts are made

the source and the drain.

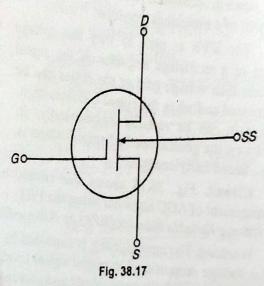

Fig. 38.17 shows the symbol of *n*-channel epletion-type MOSFET. Usually, the substrate rminal SS is internally connected to the source rminal S.

### Operation

Suppose a potential is applied to the gate such that it is positive with respect to source. Then, the outive charge on the gate attracts additional free electrons into the channel from the source. This hancement of mobile carriers decreases the channel resistance.

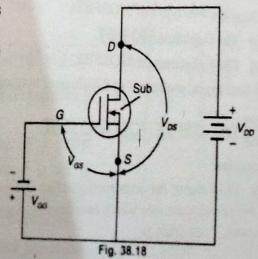

Suppose the applied voltage makes the gate negative with respect to source (Fig. 38.18). Then,

e negative charge on the gate forces free electrons at of the channel.

A carrier-depletion region is formed on the perface of the silicon at the oxide-silicon interface. The channel is thus constricted by a negative gate soltage. The resistance of the channel increases. Then the gate is sufficiently negative, the depletion erion extends completely across the channel and may with depletion region of the p-n junction on the other side of the channel. Under this condition, the channel cannot conduct current between drain and source. Thus drain and source become cut off. The negative gate voltage when channel becomes ton conducting is the pinch off voltage V<sub>p</sub>.

A positive voltage  $V_{DS}$  is also applied across the drain D and the source S (Fig. 38.18). There is a voltage drop along the channel, with the drain end of the channel positive relative to the source and. This further increases the depletion region at the surface

# 38.7.1. Static Characteristics of Depletion MOSFET

7.1. Static Characteristics of Depletion.

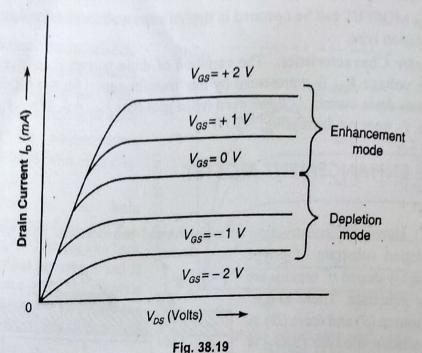

1. Output or Drain Characteristics. Fig. 38.19 shows the drain characteristic curves (In the characteristic curve versus  $V_{DS}$  at constant  $V_{GS}$ ) for an n-channel MOSEFT.

An n-channel MOSFET may be operated in either the enhancement mode or the depletion mode. The enhancement mode occurs for positive values of  $V_{GS}$  while the depletion mode occurs for negative values of  $V_{GS}$ .

When no gate-to-source voltage is applied  $(V_{GS} = 0)$ , a significant drain current  $i_D$  flows due to the flow of majority carriers (electrons) in the n-channel from source to drain under  $V_{DS}$ . As  $V_{DS}$ increases,  $i_D$  increases to a saturation value.

When the gate is made negative, positive charges are induced in the channel through the dielectric SiO2. This causes depletion of electrons (majority carriers) in the channel. Therefore, the channel becomes less conductive. Consequently, the drain current progressively decreases to almost zero as  $V_{GS}$  is made more and more negative, at all values of  $V_{DS}$

JFET, MOSFET, SCR AND UJT When the gate is made positive, negative charges are induced in the channel, thus enhancing the majority-carriers. Hence the drain current increases above its value at  $V_{GS} = 0$ , for all  $V_{DS}$

Thus, this MOSFET can be operated in depletion as well as in enhancement mode although it is termed depletion type.

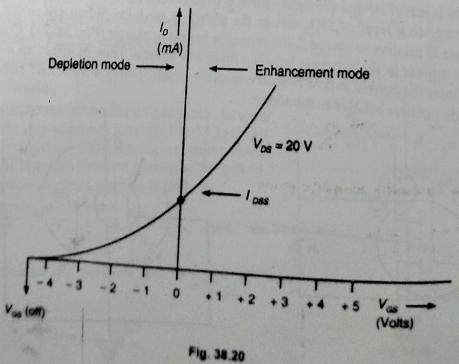

2. Transfer Characteristics. The variation of drain current  $I_D$  with gate voltage  $V_{GS}$  at a constant drain voltage  $V_{DS}$  is represented by the 'transfer curve' for the MOSFET (Fig. 38.20). It may be seen that drain current  $I_D$  flows even when gate-bias  $V_{GS} = 0$ . When  $V_{GS}$  is made more and more negative,  $I_D$  goes on decreasing.  $\gamma \gamma$

# 38.8 (THE ENHANCEMENT MOSFET

# Construction

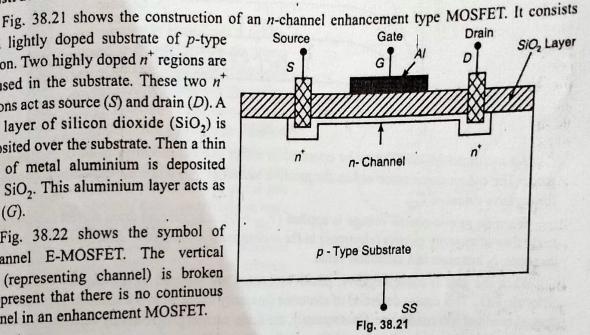

of a lightly doped substrate of p-type silicon. Two highly doped n+ regions are diffused in the substrate. These two n+ regions act as source (S) and drain (D). A thin layer of silicon dioxide (SiO2) is deposited over the substrate. Then a thin film of metal aluminium is deposited over SiO2. This aluminium layer acts as gate (G).

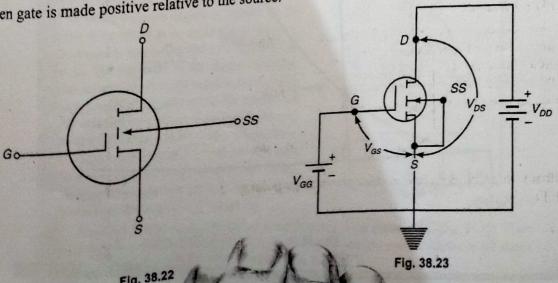

Fig. 38.22 shows the symbol of n-channel E-MOSFET. The vertical line (representing channel) is broken to represent that there is no continuous channel in an enhancement MOSFET.

### Operation

The metallic layer of Al and the upper surface of the substrate act as the parallel plates of a capacitor. The insulating layer of SiO<sub>2</sub> acts as the dielectric medium. When a positive voltage is applied to the gate G relative to source S, the capacitor begins to charge (Fig. 38.23). Consequently negative charges appear in the substrate between drain and source. Thus in effect an n-channel is created which allows the current to flow in source-to-drain circuit. Thus the MOSFET conducts only when gate is made positive relative to the source.

The MOSFET can never operate with a negative gate voltage. The MOSFET is cut-off when  $V_{GS} = 0$ .

# 38.81. Characteristics of Enhancement MOSFET

# 550 1. Output or Drain Characteristics.

Fig. 38.24 shows the drain characteristics of an *n*-channel enhancement MOSFET. Each curve shows the variation of drain current  $I_D$  with the drain-to-source voltage  $(V_{DS})$  for a fixed value of gate-to-source voltage  $(V_{GS})$ .

The magnitude of the drain current  $I_D$  is a function of  $V_{DS}$  and  $V_{GS}$ . When  $V_{GS} = 0$ ,  $I_D = 0$  because two back to back p-n junctions between S and D (one between source S and the substrate and the other between the substrate and the drain D) are reverse biased regardless of the value of  $V_{DS}$ .

DRAIN- TO-SOURCE VOLTAGE Fig. 38.24

For a fixed positive  $V_{GS}$ , the drain current first increases rapidly with  $V_{DS}$  and then saturates. It increases for higher values of  $V_{GS}$ .

The minimum positive value of  $V_{GS}$  at which the drain current is established is called the 'gatesource threshold voltage'  $V_{GST}$  or  $V_T$ .

2. Transfer Characteristics. The curve showing the variation of drain current  $I_D$  with gate-to-source voltage  $V_{GS}$  for a fixed value of  $V_{DS}$  is called the transfer characteristic. The transfer curve for an *n*-channel enhancement MOSFET is shown in Fig. 38.25.  $I_D$  flows only when  $V_{GS}$  exceeds gate-to-source threshold voltage  $V_T$ . With increase in  $V_{GS}$ ,  $I_D$  increases slowly at first and then rapidly.

## **MOSFET Biasing**

An enhancement MOSFET requires forward biasing of the gate-to-source junction. Fig. 38.26 shows a circuit arrangement for biasing an enhancement MOSFET. It provides forward biasing of the gate-to-source junction whose magnitude is given by

$$V_{GS} = \frac{R_1}{R_1 + R_f} V_{DS}$$

. Here the

feedback resistor  $R_f$  provides the operating point stability.

Fig. 38.26

### SILICON-CONTROLLED RECTIFIER (SCR)

# 38.10 SILICON-CONTROLLED RECTIFIER

The SCR is a rectifier constructed of silicon material. Silicon is chosen because of its high temperature and power capabilities.

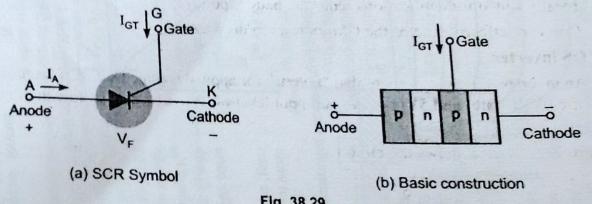

Construction: It is a four-layered device. It has three terminals. The graphic symbol for the SCR is shown in Fig. 38.29 with the corresponding connections to the four-layer semiconductor structure.

Flg. 38.29

As indicated in Fig. 38.29 a, if forward conduction is to be established, the anode must be positive with respect to the cathode. This is not, however, a sufficient criterion for turning the device on. A pulse of sufficient magnitude must also be applied to the gate to establish a turn-on gate current, represented symbolically by I'GT

### Basic operation of an SCR

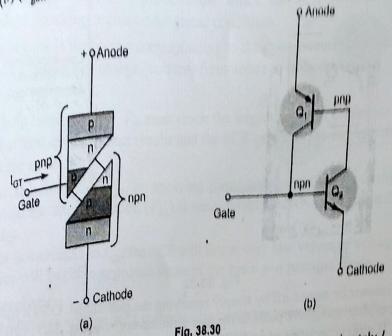

The four-layer pnpn structure of Fig. 38.29 b can be split into two three-layer transistor structures [(Fig. 38.30 (a)].

Fig. 38.30 (b) shows the SCR two-transistor equivalent circuit.

$Q_1$  is a pnp transistor.

Q, is an npn transistor.

The signal shown in Fig. 38.31 (a) is applied to the gate of the circuit of Fig. 38.30 (b).

# FET. MOSFET, SCR AND UJT

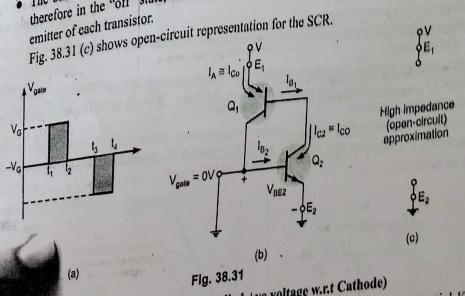

During the interval  $0 \rightarrow t_1$ ,  $V_{\text{gate}} = 0$  V, the circuit of Fig. 38.30 (b) will appear an shown in Fig. 38.31 (b) ( $V_{\text{gate}} = 0$  V is equivalent to the gate terminal being grounded). (f) "Off" state of the SCR. (When Gate is open)

For  $V_{BE_2} = V_{\text{gate}} = 0$  V, the base current  $I_{B_2} = 0$ , and  $I_{C_2}$  will be approximately  $I_{CO}$ . For  $V_{BE_2} = V_{gate}$  of  $Q_1$ ,  $I_{B_1} = I_{C_2} = I_{CO}$ , is too small to turn  $Q_1$  on. Both transistors are therefore in the "off" state, resulting in a high impedance between the collector and the

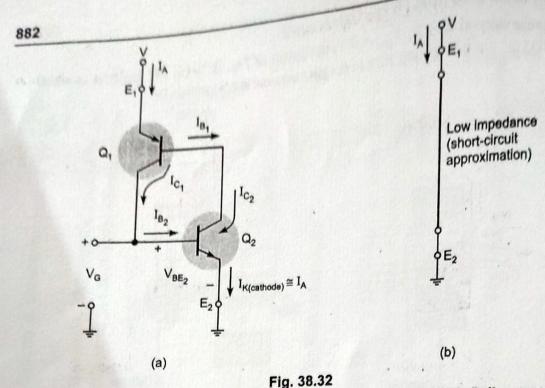

state of the SCR (When gate is applied +ve voltage w.r.t Cathode)  $V_G$ , a pulse of  $V_G$  volts will appear at the SCR gate [(Fig. 38.32 (a)]. The potential  $V_G$ The collector current of  $Q_2$  will then to a value sufficiently large to turn  $Q_2$  on  $(V_{BE_2} = V_G)$ . The collector current of  $Q_2$  will then se to a value sufficiently large to turn  $Q_1$  on  $(I_{B_1} = I_{C_2})$ .

$Q_1$  turns on,  $I_{C_1}$  will increase, resulting in a corresponding increase in  $I_{B_2}$ . The increase base current for  $Q_2$  will result in a further increase in  $I_{C2}$ .

The net result is a regenerative increase in the collector current of each transistor. The Fig. 38.32 (b) showed the resistance  $(R_{SCR} = V/I_A)$  is then small because  $I_A$  is large. Fig. 38.32 (b) shows the short-circuit representation for the SCR.

• An SCR cannot be turned off by simply removing the gate signal. Only a special few can be turned off by applying a negative pulse to the gate terminal at  $t = t_3$  [Fig. 38.31 (a)].

Volt-ampere (V - I) characteristics of an SCR

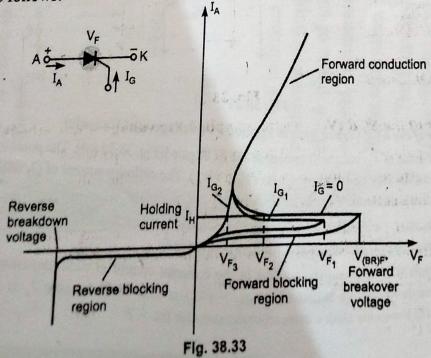

The characteristics of an SCR are provided in Fig. 38.33 for various values of gate current. It is the graph drawn between anode - cathode voltage (supply voltage)  $V_F$  and the anode current  $I_A$  for various values of gate current  $I_G$ .

### (i) Forward characteristics:

- As the supply voltage increases, the anode current remains very small at first and SCR is in the "OFF" state.

- As the supply voltage increases further, the anode current also increases. At a particular voltage  $(V_{(BR)F^*})$ , called Forward breakover voltage, SCR is turned "ON" (fired). SCR conducts heavy current.

- 1. Forward breakover voltage  $V_{(BR)F^*}$  is the voltage above which the SCR enters the conduction region. The asterisk (\*) denotes the letter to be added, which is dependent on the condition of the gate terminal as follows:

O = open circuit from G to K

S =short circuit from G to K

R = resistor from G to K

V =fixed bias (voltage) from G to K

Holding current  $I_H$  is the value of current below which the SCR switches from the  $I_{\text{con state}}$  to the forward blocking region under stated 2. Holding 1. Holding region under stated conditions. uction state to the forward blocking region under stated conditions.

Forward blocking region is the region corresponding to the open-circuit condition for the 3. For walled rectifier that blocks the flow of charge (current) from anode to cathode.

- ves for varying values of IG For the characteristic having  $I_G = 0$ ,  $V_F$  must reach the largest required breakover voltage before the "collapsing" effect results and the SCR can enter the conduction region  $(V_{(BR)F^*})$ corresponding to the on state.

- If the gate current is increased to  $I_{G1}$ , by applying a bias voltage to the gate terminal, the value of  $V_F$  required for the conduction  $(V_{Fl})$  is considerably less. Note also that  $I_H$  drops

- If the gate current is increased to  $I_{G2}$ , the SCR will fire at very low values of voltage  $(V_{F3})$ . The characteristics will begin to approach those of the basic p-n junction diode.

When anode is given negative voltage w.r.t cathode, the curve between voltage and current is

• As the reverse voltage increases, the increase in anode current is very small. At a particular wn as reverse characteristic. reverse voltage, avalanche breakdown occurs and SCR conducts heavily in the reverse direction. This maximum reverse voltage at which SCR starts conducting heavily is known

Reverse breakdown voltage is equivalent to the Zener or avalanche region of the fundamental

• Reverse blocking region is the region correponding to the open-circuit condition for the -layer semiconductor diode. controlled rectifier that blocks the flow of charge (current) from anode to cathode.

# 8.11 SCR APPLICATIONS

# Series Static Switch:

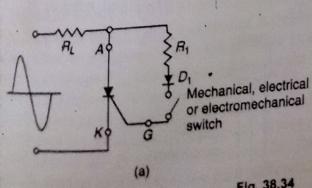

Fig. 38.34 shows a half wave series static switch.

Fig. 38.34

if the switch is closed as shown in Fig. 38.34 (b), a gate current will flow during the positive of the input signal, turning the SCR on. Resistor  $R_1$  limits the magnitude of the gate current.

Average output voltage,

$$V_{av} = \frac{1}{\pi} \int_{0}^{180^{\circ}} V_{av} \sin \theta \, d\theta = \frac{V_{av}}{\pi} \left[ \cos \alpha - \cos 180^{\circ} \right] = \frac{V_{av}}{\pi} \left( 1 + \cos \alpha \right)$$

$$\therefore \text{ Average current, } I_{av} = \frac{V_{av}}{R_{L}} = \frac{V_{av}}{\pi R_{L}} \left( 1 + \cos \alpha \right)$$

$$\Rightarrow \text{ Average current, } I_{av} = \frac{V_{av}}{R_{L}} = \frac{V_{av}}{\pi R_{L}} \left( 1 + \cos \alpha \right)$$

Thus  $I_{av}$  in full wave rectifier is two times that of half wave rectifier.

# UNIJUNCTION TRANSISTOR (UJT)

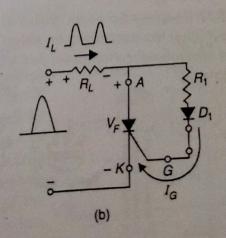

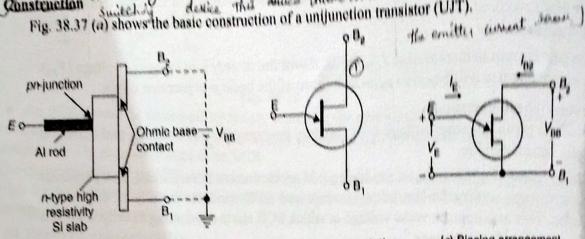

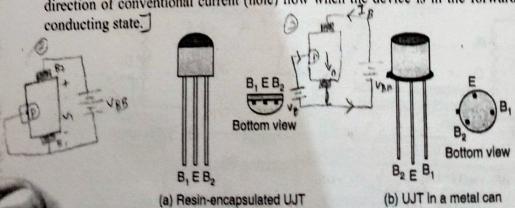

# 28.12 UNIJUNCTION TRANSISTOR (UJT) Jam terminal semilardides Construction (A Unique time hassisted and a Knee therebeath that when it is trigged Ein 18.17 (a) showed has hard a semilar and trigged Construction Fig. 38.37 (a) shows the basic construction of a unijunction transistor (UJT).

(a) Basic construction of a UJT

(b) Symbolic representation

(c) Biasing arrangement

Fig. 38.37

It is a three-terminal device. A slab of lightly doped (increased resistance characteristic) n-type silicon material has two base contacts attached to both ends of one surface and an aluminium rod alloyed to the opposite surface. The p-n junction of the device is formed at the boundary of the aluminium rod and the n-type silicon slab. The single p-n junction accounts for the terminology unijunction. The aluminium rod is alloyed to the silicon slab at a point closer to the base 2 contact than the base 1 contact. Further, base 2 terminal is made positive with respect to the base 1 terminal by  $V_{BB}$  volts.

Fig. 38.37 (b) shows the circuit symbol of a UJT. Note that the emitter leg is drawn at an angle to the vertical line representing the slab of n-type material. The arrowhead is pointing in the direction of conventional current (hole) flow when the device is in the forward-biased, active, or

The basic biasing arrangement for the unijunction transistor is provided in Fig. 38.37 (c).

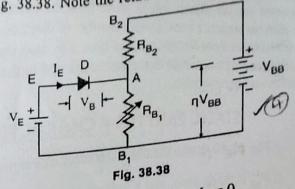

Equivalent Circuit of a UJT The circuit equivalent of the UJT is shown in Fig. 38.38. Note the relative simplicity of this slent circuit: two resistors (one fixed quivalent circuit: two resistors (one fixed, one variable) and a single diode.

The resistance of the silicon bar is represented by wo series resistors:  $R_{B_2}$  is the resistance of the base-2

The resistance  $R_{B_1}$  is shown as a variable resistor since its magnitude will vary with the current  $I_E$ . For since sentative UJT,  $R_{B_1}$  may vary from 5 k $\Omega$  down  $_{10}^{3}$  for a corresponding change of  $I_E$  from 0 to 50

The interbase resistance  $R_{BB}$  is the resistance between terminals  $B_1$  and  $B_2$  when  $I_E = 0$ . In equation form,

$$R_{BB}$$

is the resistance between  $R_{BB}$  is the resistance between  $R_{BB}$  ...(1)

$$R_{BB} = \left(R_{B_1} + R_{B_2}\right)|_{I_E = 0}$$

The position of the aluminium rod will determine the relative values of  $R_{B_1}$  and  $R_{B_2}$  with  $I_E = 0$ .

A battery  $V_{BB}$  is connected across  $B_2$   $B_1$  of equivalent circuit of UJT. Part of  $V_{BB}$  is dropped over

The magnitude of  $V_{R_{B_1}}$  (with  $I_E = 0$  i.e., emitter open) is determined by the voltage-divider rule.  $R_{B2}$  and part on  $R_{B1}$ .

with

$$I_E = 0$$

i.e., emitter open) is determined

$$V_{RB_1} = \frac{R_{B_1} V_{BB}}{R_{B_1} + R_{B_2}} = \eta V_{BB} \Big|_{I_E = 0}$$

...(2)

Here,  $\eta$  is called the *intrinsic stand-off ratio* of the device. It is defined by

rinsic stand-off ratio of the down

$$\eta = \frac{R_{B_1}}{R_{B_1} + R_{B_2}}\Big|_{I_E = 0} = \frac{R_{B_1}}{R_{BB}}$$

...(3)

For applied emitter potentials  $(V_E)$  greater than  $V_{RB_1} (= \eta V_{BB})$  by the forward voltage drop of the diode  $V_D$  (0.35  $\rightarrow$  0.70 V), the diode will fire. Assume the short-circuit representation (on an ideal basis), and  $I_E$  will begin to flow through  $R_{B1}$ . In equation form, the emitter firing potential is given

$$V_P = \eta V_{BB} + V_D$$

# OPERATION OF UJT

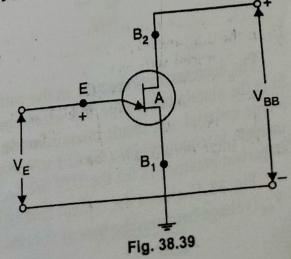

Fig. 38.39 shows the basic circuit operation of UJT.

Normally the base  $1(B_1)$  is grounded. A positive voltage when there is no emitter  $(B_1)$  is grounded. When there is no emitter  $(B_2)$ . When there is no emitter surrent, this voltage  $V_{BB}$  produces a uniform drop across the 5000 to 10 ccc. 5000 to 10,000 ohms internal resistance of silicon bar. The resultant current through the bar will produce a voltage drop A  $V_{88}$  between points A and  $B_1$  of the bar where A denotes the point, where the P region is formed. So long as the where the P region is formed.

The applied to the emitter with respect to  $B_1$  is less than V.  $V_A$  or  $V_P$  (=  $\eta$   $V_{BB}$ ), the p-n junction remains reverse

MODERN PHYSICS biased and only a very small reverse current I<sub>E</sub> flows in the emitter circuit. However, at the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase is quite steep because this current is the increase and the increase and the increase and the increase is quite steep because this current is the increase and the increase are increased and the increase and the increase and the increase are increased and the increase and the increase are increased and the increased are increased are increased and the increased are increased and the increased are increased are biased and only a very small reverse current  $I_g$  the junction becomes forward biased and only a very small reverse greater than  $\eta V_{gg}$ , the junction becomes forward biased biased and only a very small reverse greater than  $\eta V_{gg}$ , the junction becomes forward biased biased and only a very small reverse greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse current  $I_g$  becomes greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse current  $I_g$  becomes greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse current  $I_g$  becomes greater than  $\eta V_{gg}$ , the junction becomes forward biased and only a very small reverse current  $I_g$  becomes greater than  $\eta V_{gg}$ , the junction becomes forward biased and  $I_g$  becomes greater than  $I_g$  becomes greater tha biased and only a very small becomes greater than 17 gg becomes greater than 17 gg becomes the entire voltage 1'g becomes greater than 17 gg becomes the increase is quite steep because this current is due increased and and and and an entire to base 1. The presence of the log to the holes where the silicon, which move from the emitter to base 1. The presence of these holes we holes to the silicon and the silicon which number of electrons to this region and, in consequent the emitter voltage 1/2 increases. The increase is quite to base 1. The presence of the lot the least sincrease is quite to base 1. The presence of these to the least sincrease in the injected into the silicon, which move from the emitter to base 1. The presence of these to the least in the injected into the silicon, which move from the emitter to base 1. The presence of these to the least in the injected into the silicon, which move from the emitter to base 1. The presence of these to the least in the injected into the silicon, which move from the emitter to base 1. The presence of these to the least in the injected into the silicon, which move from the emitter to base 1. The presence of these to the least injected into the silicon, which move from the emitter to base 1. The presence of these to the least injected into the silicon, which move from the emitter to base 1. The presence of these to the least injected into the silicon, which move from the emitter to base 1. The presence of these to the least injected into the silicon, which move from the emitter to base 1. The presence of these to the least injected into the silicon injected i eminer current Iz increase, which move from the entitle of this region and, in consequence, in the injected into the silicon, which move from the entitle of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and, in consequence, in the silicon bar amuch a considerable number of electrons to this region and in the consequence of the silicon bar amuch a considerable number of electrons to the silicon bar amuch a considerable number of electrons to the silicon bar amuch a considerable number of electrons to the silicon bar amuch a consequence of the silicon bar a injected into the silicon, injected into the silicon bar armsets a considerable number of electron sharply. The upshot is that an increase in the bar resistance between emitter and base 1 to drop sharply. The upshot is that an increase in the bar resistance between emitter and base 1 to drop sharply. The upshot is that an increase in the bar resistance and in the emitter voltage, which is known as a new courses a decrease in the resistance and in the emitter voltage, which is known as a new courses a decrease in the resistance and in the emitter voltage. bar resistance between emitter and base 1 to drop solution bar resistance between emitter and in the emitter voltage, which is known as a negative

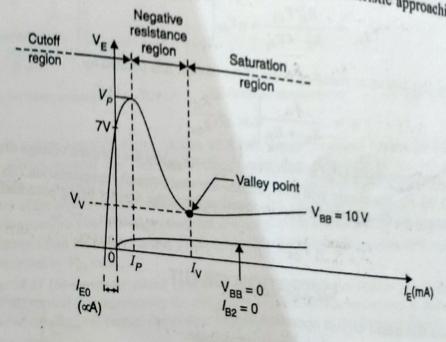

# STATIC EMITTER - CHARACTERISTIC CURVE FOR A UJT

Fig. 38.40 shows the characteristics of a representative unijunction transistor for  $V_{BB} = 10 V_{c}$ , the resulting current  $I_{c}$  there. Fig. 38.40 shows  $I_E$  is made zero, and a voltage is applied to  $V_E$ , the resulting current  $I_E$  that flows gives the emitter to base-1 diode characteristic  $(I_{R2} = 0)$ .

Note that for emitter potentials to the left of the peak point, the magnitude of  $I_E$  is never (measured in microamperes). The current  $I_{E0}$  corresponds very closely note. Note that for emitter potentials greater than  $I_{E0}$  (measured in microamperes). The current  $I_{E0}$  corresponds very closely with the greater than  $I_{E0}$  (measured in Indexensian Indexe reverse leakage current  $I_{CD}$  of the constraint  $I_{E}$  of the current  $I_{E}$ . After  $V_{P}$ , an attempt to increase  $V_{E}$  is followed by a corresponding decrease in  $V_{E}$ . This corresponds region. Conduction is established at  $I_E$  with a corresponding decrease in  $V_E$ . This corresponds to a substance region. After the negative resistance region, the valley point is reached  $v_E$ . sudden increase in ellitter current and sudden increase in ellitter the negative resistance region, the valley point is reached. Further in L. places the device in the saturation region (with characteristic approaching to increase in I<sub>E</sub> places the device in the saturation region (with characteristic approaching that of a

The decrease in resistance in the active region is due to the holes injected into the n-type slab from the aluminium p-type rod when conduction is established. The increased hole content in the n-type material will result in an increase in the number of free electrons in the slab, producing in conductivity (2). Three other increase in conductivity (G) and a corresponding drop in resistance  $(R \downarrow = 1/G \uparrow)$ . Three other important parameters for the LLC. important parameters for the UJT are  $I_p$ ,  $V_v$  and  $I_v$ . Each is indicated on Fig. 38.40.

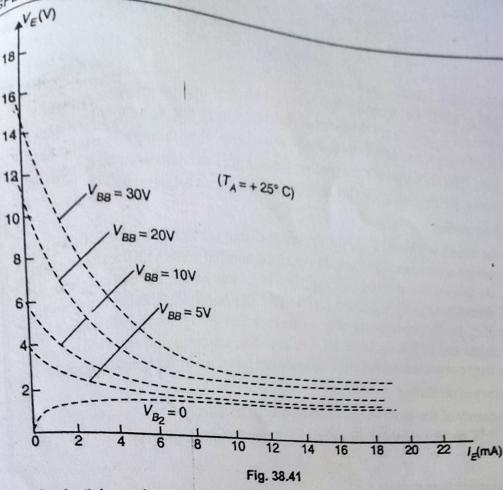

Fig. 38.41 shows the typical family of static emitter characteristic curves of a UJT for various (voltage between the typical family of static emitter characteristic curves of a UJT for various V<sub>BB</sub> (voltage between the bases) values.

Note that  $I_{E0}$  ( $\mu A$ ) is not in evidence since the horizontal scale is in milliamperes.

The intersection of each curve with the vertical axis is the corresponding value of  $V_P$ . For fixed alues of  $\eta$  and  $V_D$ , the magnitude of  $V_P$  will vary as  $V_{BB}$ , that is,

$$V_{P} \uparrow = \eta V_{BB} \uparrow + V_{D}$$

fixed

# 38.13 APPLICATIONS OF UJT

# (1) UJT relaxation oscillator

The UJT can be used in a single stage oscillator circuit to provide a pulse signal suitable for digital-circuit applications.

### Circuit Details

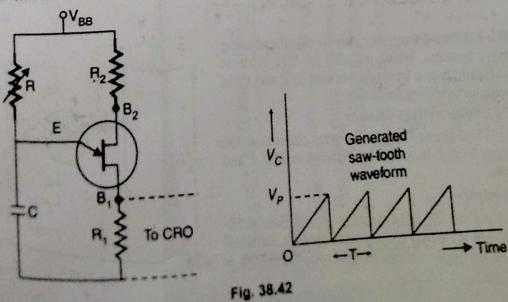

Fig. 38.42 shows the circuit of the UJT relaxation oscillator.

It consists of a UJT and a capacitor C which is charged through a variable resistance R and  $R_2$  are the external resistances such that  $R_1 << R_2$ .  $R_1$  is less than to MODERN PHYSICS It consists of a UJT and a capacitor C which is such that  $R_1 << R_2$ .  $R_1$  is less than C0 R1 is less than R2 are the external resistances such that  $R_1 << R_2$ .  $R_1$  is less than R3 is switched on.  $R_2$  are the external resistances such that  $R_1 << R_2$ .  $R_1$  is less than R3 is switched on.  $R_2$  are the external resistances such that  $R_1 << R_2$ .  $R_2$  is less than R3 is switched on.  $R_3$  is less than  $R_3$ 3 is less than  $R_4$ 3 is less than  $R_4$ 4 is less than  $R_4$ 5 is less  $V_{BB}$  is switched on.  $R_1$  and  $R_2$  are the external resistance provide spike waveforms. Here the negative resistance region of these resistance provide spike waveforms. Here the negative resistance region of the inclusion of these resistance of the capacitor through UJT develops a saw-tooth output. Resistance region of the capacitor through UJT develops a saw-tooth output. The inclusion of these resistances provide spine the inclusion of these resistances provide spine the UJT develops a saw-tooth output. Resistor through UJT develops a saw-tooth output. Resistor

Circuit operation

When the circuit is switched on, the capacitor C starts charging through R. During charging through R capacitor increases in an exponential relation till it reaches the peak R peak When the circuit is switched on, the capacitor increases in an exponential relation till it reaches the peak point of time, UJT switches to its low resistance conducting mode. period, the voltage across capacitor increases with period, the voltage  $V_P$ . At this instant of time, UJT switches to its low resistance conducting mode,  $S_0$ , the voltage  $V_P$ . At this instant of time, UJT and  $R_1$ . Discharge time constant is very small, the voltage  $V_p$ . At this instant or time, of I and I Discharge time constant is very small due to capacitor I discharges abruptly. As the capacitor voltage moves back to zero, the capacitor C discharges suddenly unedge. So capacitor voltage moves back to zero, the emitter small value of  $R_1$ . So C discharges abruptly. As the capacitor voltage moves back to zero, the emitter and LHT is switched off. The capacitor starts charging again and the next small value of  $R_1$ . So C discnarges accuracy. The capacitor starts charging again and the emitter ceases to conduct and UJT is switched off. The capacitor starts charging again and the next cycle ceases to conduct and UJT is switched off. The capacitor starts charging again and the next cycle begins. The output saw-tooth waveform frequency can be varied by changing the value of R.

### Frequency of oscillation

The frequency of saw-tooth wave can be calculated as follows:

The voltage across capacitor during charging at any instant t is given by

$$v_c = V_{BB} \left( 1 - e^{-t/\tau} \right)$$

where  $\tau$  is charging time constant = R C.

This voltage is applied to the emitter. So

$$v_c = V_E = V_{BB}(1 - e^{-t/\tau})$$

When capacitor charges to peak voltage  $V_P$ , UJT triggers. The UJT triggers when  $V_P = \eta V_{BP}$ If the capacitor takes a time T to charge to firing potential  $V_P$ , then

$$V_{P} = V_{BB}(1 - e^{-T/CR})$$

or

$$\frac{V_{P}}{V_{BB}} = \eta = (1 - e^{-T/CR})$$

or

$$e^{-T/CR} = 1 - \eta'$$

or

$$T = CR \log_{e} \left(\frac{1}{1 - \eta}\right)$$

Frequency of oscillation,

$$f = \frac{1}{T} = \frac{1}{RC \log_e \left(\frac{1}{1-\eta}\right)}$$

.

The oscillating frequency may be calculated using the above equation, which includes the UJT intrinsic stand-off ratio  $\eta$  as a factor (in addition to R and C) in the oscillator operating frequency.

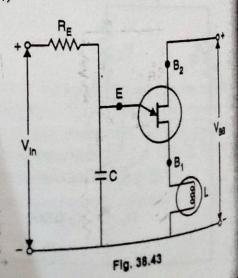

### (2) UJT as over voltage detector

Fig. 38.43 shows a simple d.c. over voltage detector. A warning lamp L is connected between emitter E and B, circuit.

### Principle

As long as the input voltage is less than peakpoint voltage Vp of UJT, the device remains switched off. When the input voltage exceeds Vp, the device is switched on.

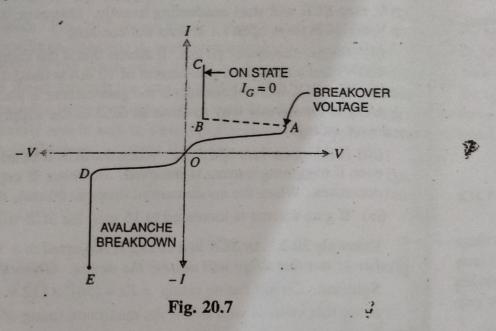

# 20.5 V-I Characteristics of SCR V 5

Vino R IG

It is the curve between anode-cathode voltage (V) and anode current (I) of an SCR at constant gate current. Fig. 20.7 shows the V-I characteristics of a typical SCR.

Fig. 20.6

(i) Forward characteristics. When anode is positive w.r.t. cathode, the curve between V and I is called the forward characteristic. In Fig. 20.7, OABC is the forward characteristic of SCR at  $I_G = 0$ . If the supply voltage is increased from zero, a point is reached (point A) when the SCR starts conducting. Under this condition, the voltage across SCR suddenly drops as shown by dotted curve AB and most of supply voltage appears across the load resistance  $R_L$ . If proper gate current is made to flow, SCR can close at much smaller supply voltage.

(ii) Reverse characteristics. When anode is negative w.r.t. cathode, the curve between V and I is known as reverse characteristic. The reverse voltage does come across SCR when it is operated with a.c. supply. If the reverse voltage is gradually increased, at first the anode current remains small (i.e. leakage current) and at some reverse voltage, avalanche breakdown occurs and the SCR starts conleakage current) and at some reverse voltage, avalanche breakdown occurs and the SCR starts conducting heavily in the reverse direction as shown by the curve DE. This maximum reverse voltage at

which SCR starts conducting heavily is known as reverse breakdown voltage.

## 20.6 SCR in Normal Operation

In order to operate the SCR in normal operation, the following points are kept in view:

- (i) The supply voltage is generally much less than breakover voltage.

- (ii) The SCR is turned on by passing an appropriate amount of gate current (a few mA) and not by breakover voltage.

- (iii) When SCR is operated from a.c. supply, the peak reverse voltage which comes during negative half-cycle should not exceed the reverse breakdown voltage.

- (iv) When SCR is to be turned OFF from the ON state, anode current should be reduced to holding current.

- (v) If gate current is increased above the required value, the SCR will close at much reduced supply voltage.

### 20.7 SCR as a Switch

The SCR has only two states, namely; ON state and OFF state and no state inbetween. When appropriate gate current is passed, the SCR starts conducting heavily and remains in this position indefinitely even if gate voltage is removed. This corresponds to the ON condition. However, when the anode current is reduced to the holding current, the SCR is turned OFF. It is clear that behaviour of SCR is similar to a mechanical switch. As SCR is an electronic device, therefore, it is more appropriate to call it an electronic switch.

- S Advantages of SCR as a switch. An SCR has the following advantages over a mechanical of electromechanical switch (relay):

- (i) It has no moving parts. Consequently, it gives noiseless operation at high efficiency.

- (ii) The switching speed is very high upto 109 operations per second.

- (iii) It permits control over large current (30–100 A) in the load by means of a small gate current (a few mA).

- (iv) It has small size and gives trouble free service.